TL;DR

Xsight Labs demonstrated its E1 DPU, a 64-core Arm Neoverse N2 device built on TSMC 5nm with two 400G MACs for 800Gbps of networking. The platform combines DDR5 memory, PCIe Gen5 connectivity and an architecture that runs networking on the CPU cores rather than dedicated NIC IP, and has passed SONiC-DASH 800G validation with reported headroom.

What happened

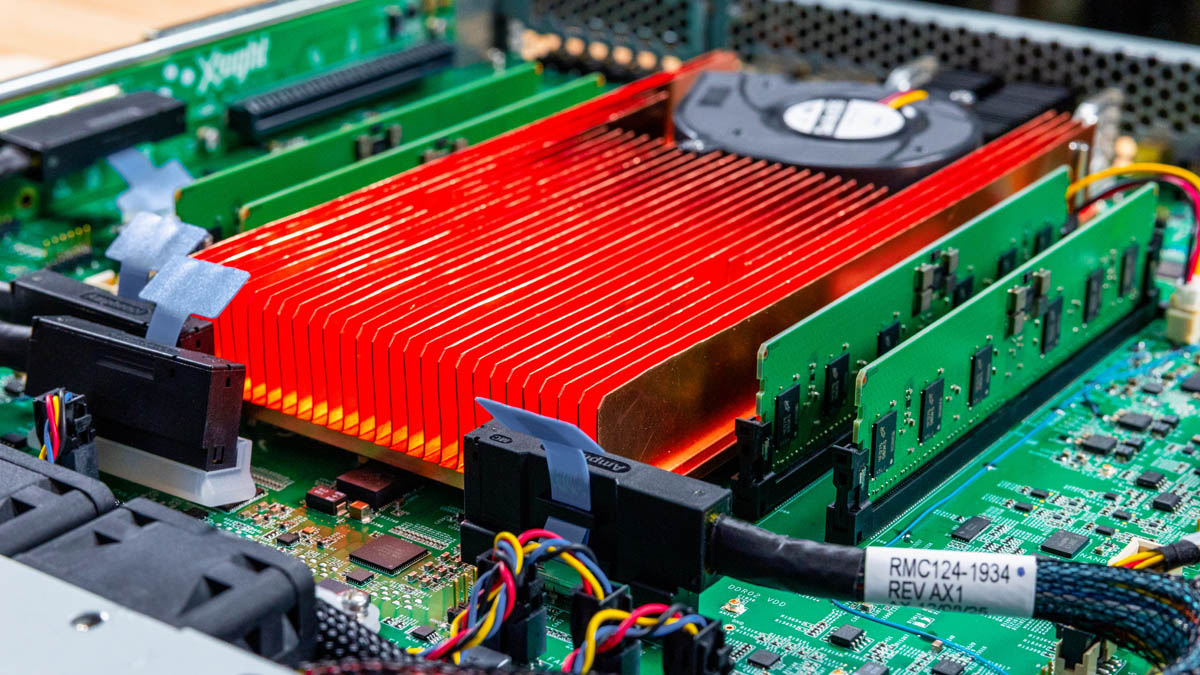

Xsight Labs brought its E1 DPU into a lab and 1U development chassis for early evaluation. The E1 integrates 64 Arm Neoverse N2 cores fabricated on TSMC's 5nm process, supports up to four DDR5-5200 ECC RDIMMs, and exposes two QSFP112 400Gbps ports for a total of 800Gbps. Unlike many DPUs that pair NIC IP with host cores, the E1 uses its Neoverse N2 cores (with DPDK support) to handle packet processing. The company reports the unit passed the SONiC-DASH Hero 800G test with roughly 19% headroom, indicating capacity beyond the validated load. The chassis version also exposes multiple PCIe Gen5 lanes and front dual-slot x16 slots with bifurcation options, enabling direct attachment of SSDs, GPUs or other accelerators. Xsight presented an example sled-based deployment that aggregates multiple E1s into a 1OU server with many SSDs and a combined pool of Arm cores.

Why it matters

- Reframes the DPU role from a NIC adjunct to a compact server capable of handling both networking and application tasks.

- Running packet processing on Neoverse N2 cores (with DPDK) may free cycles for additional workloads since no separate NIC IP is used.

- SONiC-DASH 800G validation with reported headroom demonstrates the platform can sustain high connection counts and throughput under an open-source NOS.

- Flexible PCIe Gen5 connectivity and slot bifurcation let system designers attach storage, accelerators or GPUs directly behind the DPU for disaggregated architectures.

Key facts

- Processor: 64-core Arm Neoverse N2 implemented on TSMC 5nm.

- Networking: two 400G MACs (QSFP112) for a combined 800Gbps throughput.

- Memory: supports four DDR5-5200 ECC RDIMMs in the 1U platform.

- PCIe: exposes PCIe Gen5 lanes with dual-slot front x16 connectors and x16 or x4/x4/x4/x4 bifurcation options.

- Software/stack: uses DPDK and the Neoverse N2 cores to perform networking rather than separate NIC IP.

- Validation: reported passing the SONiC-DASH Hero 800G test with ~19% headroom.

- Form factors shown: a PCIe card and a larger 1U development chassis; sled-based 1OU example aggregates five sleds into 320 cores and forty SSDs.

- Development platform cues: visible USB headers and other dev-focused features on the unit shown.

What to watch next

- Xsight's follow-up article demonstrating OS installation from an ISO on the E1 platform (planned next piece).

- Further optimizations to increase performance headroom and real-world workload validation under SONiC and other NOSes.

- Commercial availability and general availability (GA) timing for the E1 DPU: not confirmed in the source.

Quick glossary

- DPU: Data Processing Unit — a programmable processor designed to offload networking, storage, and security tasks from the host CPU.

- Arm Neoverse N2: A high-performance Arm CPU microarchitecture aimed at cloud and infrastructure workloads; used here as the E1's CPU cores.

- PCIe Gen5: The fifth generation of the PCI Express interconnect, offering higher per-lane bandwidth than prior generations for devices like GPUs and NVMe SSDs.

- SONiC: Software for Open Networking in the Cloud — an open-source network operating system widely deployed for large-scale switching and routing.

- DPDK: Data Plane Development Kit — a set of libraries and drivers for fast packet processing in user space, often used to accelerate networking on general-purpose CPUs.

Reader FAQ

What is the peak network bandwidth of the E1 DPU?

The E1 exposes two 400Gbps MACs for a combined 800Gbps of networking.

Does the E1 rely on separate NIC IP for packet processing?

No. According to the source, the E1 uses its Arm Neoverse N2 cores with DPDK to perform networking rather than a distinct NIC IP block.

How much memory does the platform support?

The 1U platform supports up to four DDR5-5200 ECC RDIMMs.

Is the E1 generally available for purchase?

not confirmed in the source

Can the E1 act as a PCIe root for attached devices?

Yes. The E1 can function in both roles and supports x16 or x4/x4/x4/x4 bifurcation for its slots.

NetworkingServerServer CPUs This is the Xsight Labs E1 DPU A 64-core Arm Neoverse N2 800G DPU By Patrick Kennedy – January 3, 2026 0 Xsight Labs E1 HeatSink 6 Today…

Sources

- Xsight Labs E1 DPU a 64-Core Arm Neoverse N2 800G DPU

- E-Series

- This is the Xsight Labs E1 DPU A 64-core Arm Neoverse N2 …

- E1-SoC Product Brief – June 2025

Related posts

- FP-pack: Functional pipelines in TypeScript emphasizing pipe, async and SideEffect

- C3: An Ergonomic, Safe and Familiar Evolution of the C Language

- Mui Board — a minimalist, screen‑free smart home controller crafted from wood